宜特指出,功率半導體進行“減薄”,一直都是改善工藝,使得功率組件實現“低功耗、低輸入阻抗”最直接有效的方式。晶圓減薄除了有效減少后續封裝材料體積外,還可因降低RDS(on)(導通阻抗)進而減少熱能累積效應,以增加芯片的使用壽命。

但如何在減薄工藝中降低晶圓厚度,又同時兼顧晶圓強度,避免破片率居高不下之風險自晶圓減薄最大的風險。

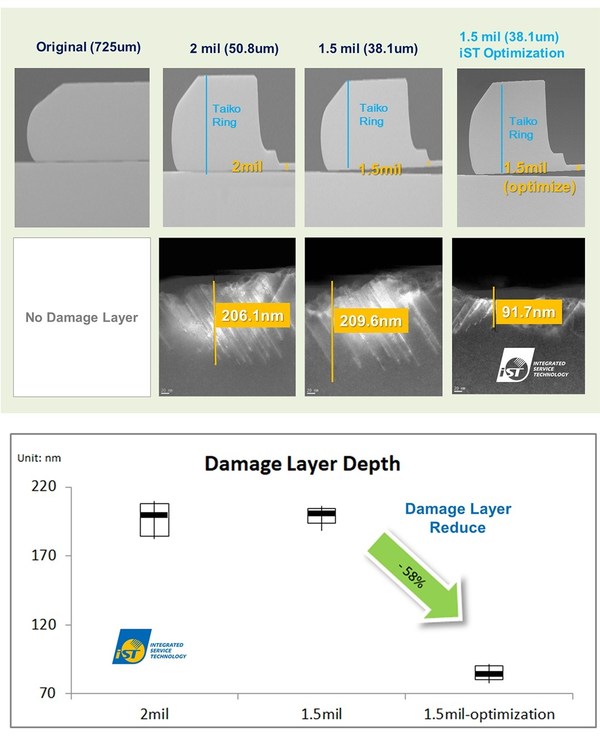

為解決此風險,iST宜特領先業界,已完成2mil(50um)、1.5mil(38um),甚至到0.4mil(10um)減薄技術開發,iST宜特更藉由特殊的優化工藝,在降低晶圓厚度的同時,也兼顧晶圓強度,可將研磨損傷層(Damage layer)降到最低。

關于宜特科技

始創于1994年,iST宜特從 IC 線路除錯及修改起家,逐年拓展新服務,包括失效分析、可靠性驗證、材料分析等,建構完整驗證與分析工程平臺與全方位服務。客群囊括電子產業上游 IC 設計至中下游成品端,并建置車用電子驗證平臺、高速傳輸信號測試。宜特秉持著提供客戶完整解決方案的宗旨,從驗證領域,跨入“晶圓后端工藝整合”量產服務。更多訊息請上官網 https://www.istgroup.com

]]>