上海2022年12月21日 /美通社/ -- 世芯電子正式宣布以貢獻者(Contributor)會員身份加入UCIe?(Universal Chiplet Interconnect Express?)產業聯盟,參與UCIe技術標準的研究,結合本身豐富的先進封裝(2.5D及CoWoS)量產及HPC ASIC設計經驗,將進一步鞏固其高性能ASIC領導者的地位。

UCIe可滿足來自不同的晶圓廠、不同工藝、有著不同設計的各種chiplet芯片的封裝需求。它是一種開放的行業互聯標準,可在Chiplet之間提供高帶寬、低延遲、節能且具有成本效益的封裝連接,使得開放的Chiplet生態系統得以實現。世芯作為貢獻者會參與到技術工作組當中,且積極影響未來chiplet技術的發展方向。

UCIe 作為一先進的技術聯盟,對于世芯及其高性能計算ASIC客戶來說意義非凡,因它設法解決了對計算、內存、存儲和跨越云、邊緣、企業、5G、汽車及高性能計算的整個計算連續體的連接性的不斷增長的需求。世芯電子總裁兼首席執行官沈翔霖表示:“UCIe對先進技術ASIC的未來至關重要,世芯積極參與將勢在必行。加入UCIe產業聯盟,世芯會扮演技術標準的積極貢獻者,也會是帶領高階HPC ASIC芯片設計邁向實現Chiplet里程碑的重要廠商。”

更多關于世芯電子請至公司網站:http://www.alchip.com

]]>上海2022年7月7日 /美通社/ -- 近年來先進封裝(Advanced Package)成為了高性能運算客制化芯片(High Performance Computing ASIC)成功與否的關鍵。隨著市場需求不斷升級,世芯電子致力于投資先進封裝關鍵技術,將其更有效率的整合到芯片設計供應鏈中, 以實現全客制化的合作模式。

隨著高階應用市場的發展,科技系統大廠開始必須透過軟硬體系統整合來實現創新,使其產品達到更強大的功能與強化的系統效能。也因為如此,現今各個系統大廠與OEM對客制化芯片(ASIC)的需求呈現高度成長。特別是在高性能運算系統芯片(SoC)領域,IC設計本身非常復雜且成本已經相當昂貴,如果再加上后端設計包含封裝,測試,供應鏈整合等等會是更大規模的投資。在成本及效率的考慮下,各大企業選擇與專業高階ASIC設計公司合作已是必然的趨勢。

高性能運算IC的成功關鍵取決于先進封裝技術

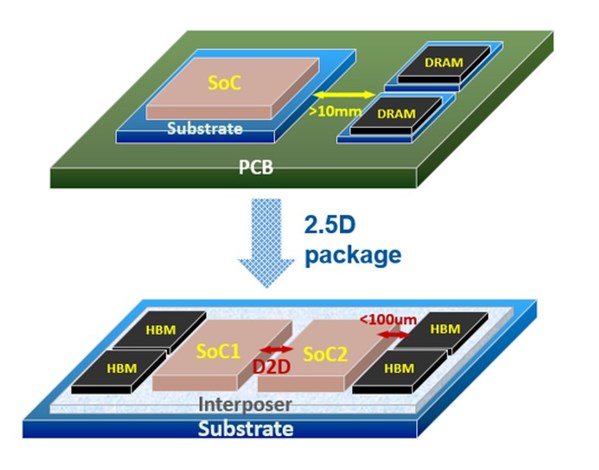

高階應用市場的高性能運算系統芯片成長強勁,伴隨的是前所未有對先進封裝技術的依賴。由臺積電所研發的先進封裝技術CoWoS 及InFO 2.5D/3D封裝對于成功部署當今的HPC SoC ASIC至關重要。CoWoS封裝可以實現把數個小芯片(Chiplets)黏合在同一中介片(Interposer)同一封裝基板(Substrate)上,以達到“系統級微縮”的境界,大大提升了SoC之間互連密度和性能,是科技史上的一大突破。另一先進封裝技術為多芯片模組(Multi-Chip-Module,簡稱MCM)也是類似概念。與傳統封裝不同,先進封裝需要與電路設計做更多的結合,加上必須整合產業的中下游,對設計整合能力是一大挑戰,也是門檻相當高的投資。

世芯看到了高性能系統運算ASIC設計服務市場對先進封裝需求的急速成長。“如今,各個科技大廠正大量投資于IC前端設計,以求跟自家產品完美結合以最大程度區別市場差異性及市場領先地位。他們此刻需要的是與杰出的專業ASIC設計服務公司合作,才不會讓他們的大量投資及時間成本付諸流水。”世芯電子總裁兼首席執行官沈翔霖說到。

世芯是客戶在高性能運算市場客制化芯片的重要伙伴

世芯電子提供的高性能運算設計方案能無縫整合高性能運算系統芯片設計和先進封裝技術。世芯的MCM 于2020年量產,CoWoS 于2021 年量產。現有大尺寸系統芯片幾乎是光罩的最大尺寸(Reticle Size,800mm2)。 中介片(Interposer)設計為 3~4倍于光罩最大尺寸(3~4X Reticle Size),而先進封裝尺寸甚至達到 85x85mm2是現有封裝技術的極限。這都是經過多項客戶產品成功量產驗證過的。也證明了世芯的高性能運算設計方案滿足高性能運算IC市場需求,是其取得市場領先地位的重要關鍵。

世芯電子股份有限公司成立于2003年,總部設于臺北。提供系統公司高復雜度、高產量SoC設計及量產服務。產品的應用市場包含AI人工智能、HPC高性能運算、娛樂機臺、手機、通訊設備、電腦及其他消費性電子IC產品。世芯致力于為客戶提供最高效益/成本比的解決方案,確保客戶一次投片成功并快速將產品導入市場。世芯成立以來,已完成眾多高階制程(16納米以下),高性能運算HPC SoC IC及先進封裝(CoWoS,2.5D)量產的成功案例,并于2014年10月28日于臺灣證券交易所掛牌上市(股票代號:世芯-KY: 3661)。目前在美國(硅谷)、日本(新橫濱)、中國大陸(上海、無錫、合肥、廣州、濟南、北京)和中國臺灣(新竹)擁有分部。

擁有一套經過自身驗證的芯片設計流程和法則,是世芯成功的關鍵。它不僅能優化功耗、性能和面積的設計,同時還能符合客戶嚴格的流片計劃要求。世芯完整的7/6/5納米設計能力包括大規模芯片設計里必要的分區和簽核、測試設計流程,以及一套涵蓋了全面系統協同設計簽核的中介層/基板設計的完整2.5D封裝設計流程。

世芯的創新封裝服務也涵蓋信號/電源仿真及熱仿真(SI/PI),能提供即插即用的流片后解決方案,以減少基板層和由此產生的材料成本。這樣產生的7/6/5納米IC具有更精確的功率和熱估算流程,能避免流片后的失敗,在高功率設計中尤其關鍵。

世芯完整的5納米“設計到交付”方法側重于最大限度地縮短設計周期。其中的實體設計像是芯粒(Chiplet)技術平臺、高性能計算IP組合含世芯的D2D APLink IP、IP子系統集成服務,以及最新的2.5D異構封裝技術等。

“世芯的優勢一直是先進工藝芯片設計。在7納米系統芯片項目的設計流片量產上,我們與客戶再次合作并取得了100%的流片成功率。”世芯總裁兼首席執行官沈翔霖表示,“我們的設計和驗證法則乃經過嚴格認證,亦源于我們企業文化一貫秉持的核心服務理念。”

了解更多信息,請至公司網站:http://www.alchip.com

關于世芯電子

世芯電子股份有限公司成立于2003年,總部設于臺北。提供系統公司高復雜度、高產量SoC設計及量產服務。產品的應用市場包含AI人工智能、HPC高速運算、娛樂機臺、手機、通訊設備、超級計算機及其他消費類電子IC產品。世芯致力于為客戶提供最高效益/成本比的解決方案,確保客戶一次投片成功并快速將產品導入市場。世芯成立以來,已完成眾多高階制程(16納米以下)及高復雜度SoC設計的成功案例,并于2014年10月28日于臺灣證券交易所掛牌上市(股票代號:世芯-KY: 3661),是臺積電認證的價值鏈合作伙伴(VCA)。目前在美國(硅谷)、日本(新橫濱)、中國內地(上海、無錫、合肥、廣州、濟南、北京)和臺灣(新竹)擁有分部。

在臺積電 2021 年開放創新平臺的技術演講中,James Huang 強調,芯粒和先進封裝提供了與單片 SoC 相比具有競爭力的成本結構,同時保持了相近的性能和功耗。

James Huang 引用了兩項對芯粒/封裝發展至關重要的技術:一種是臺積電的 3DFabric 和 CoWos® 組合技術。 另一個是世芯的 APLink 芯粒間互聯 I/0。

APLink 芯粒間互聯 I/0 支持多個芯粒之間的高速數據交換。APLink 1.0 的目標是臺積電的 12 納米工藝,而 APLink 2.0 的目標為7納米工藝。5納米工藝的APLink 3.0目前正在進行測試芯片結果評估,已達到目標線速。APLink1.0和2.0的線路速率分別為1Gbps和4Gbps。

超越眼前的視野,James Huang 向與會者展示了未來的高峰。在詳細介紹 APLink 4.0 時,他透露了以 3 納米為目標的芯粒間互聯 IP。

APLink 4.0 的互連將采用以標準內核電壓運行的源同步 I/O 總線。每個 PHY 模塊以 12Tbps 的速度運行,每條 DQ 線路的速度高達 16Gbps,但只有 5 納秒的延遲。這些規格能支持可靠的系統操作。

APlink 4.0 IP 將支持北/南和東/西方向以及對稱的 PHY 布局排列,這最大限度地減少芯粒間互聯的信號線長度。

“真正將未來變為現實的是一種靈活的商業模式,它更符合未來技術創新需求。”James Huang 指出。

在實現多芯粒系統設計時,世芯與客戶的合作模式提供多個起始點,包含產品規格制訂、SoC 設計或系統調試與量產等合作起始點。

如需更多信息,請訪問 www.alchip.com。

關于世芯電子

世芯電子股份有限公司成立于 2003 年,總部設于臺北。提供系統公司高復雜度、高產量 SoC 設計及量產服務。產品的應用市場包含 AI 人工智能、HPC 高速運算、娛樂機臺、手機、通訊設備、計算機及其他消費性電子 IC 產品。世芯致力于為客戶提供最高效益/成本比的解決方案,確保客戶一次投片成功并快速將產品導入市場。世芯成立以來,已完成眾多高階制程(16 納米以下)及高復雜度 SoC 設計的成功案例,并于 2014 年 10 月 28 日于臺灣證券交易所掛牌上市(股票代號:世芯-KY: 3661)。目前在美國(硅谷)、日本(新橫濱)、中國大陸(上海、無錫、合肥、廣州、濟南、深圳)和臺灣(新竹)擁有分部。